痞子衡嵌入式:串行EEPROM接口事实标准及SPI EEPROM简介

痞子衡 人气:15大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家介绍的是EEPROM接口标准及SPI EEPROM。

痞子衡之前写过一篇文章 《SLC Parallel NOR简介》,介绍过并行NOR Flash基本概念。众所周知,现如今嵌入式非易失性存储器基本被NOR Flash一统江湖了,但在Flash技术发明之前,EEPROM才是非易失性存储器的霸主。EEPROM的全称是"电可擦除可编程只读存储器",即Electrically Erasable Programmable Read-Only Memory,EEPROM技术的发明可是拯救过一大批嵌入式工程师的,毕竟在这之前非易失性存储器技术的演进分别是ROM(只读), PROM(只能写一次), EPROM(紫外线可擦除),擦除方式都不太友好,直到EEPROM的出现才变得人性化。虽说现在Flash是主流,但在较低容量(2Mb以下)尤其是超低容量(1Kb以下)的市场,EEPROM仍然有其不可替代的应用场合。今天痞子衡就来好好聊一聊EEPROM:

一、EEPROM背景简介

聊到EEPROM发展史,不得不提浮栅MOSFET,这是一项发明于1967年的技术,它是所有闪存的基础。1970年,第一款成功的浮栅型器件-EPROM被发明。1979年,大名鼎鼎的SanDisk(闪迪)创始人Eli Harari,发明了世界上首个电可擦除的浮栅型器件即EEPROM。

讲到EEPROM必然要将它和与其相爱相杀的Flash一起对比。关于Flash大家都很熟悉,但其实Flash全称应该叫Flash EEPROM,它属于广义的EEPROM。而本文主角EEPROM,指的是狭义的EEPROM,Flash和EEPROM最大的区别是:Flash按扇区操作,EEPROM按字节操作。Flash的特点是结构简单,容量可以做得比较大且在大数据量下的操作速度更快,但缺点是操作过程麻烦,所以Flash适于当不需频繁改写的程序存储器。而在有些应用中往往需要频繁的改写某些小量数据且需掉电非易失,传统结构的EEPROM则非常适合。

EEPROM不像NOR, NAND Flash技术演进得那么复杂,因此实际上关于EEPROM并没有成文的标准,即使最知名的电子行业标准之一JEDEC也没有关于EEPROM的标准出台,不过各大厂商生产的EEPROM似乎都遵从某种约定的事实标准,这在后面介绍的EEPROM接口命令里显得尤为明显。

二、Serial EEPROM原理

2.1 Serial EEPROM分类

从软件驱动开发角度而言,Serial EEPROM可以从以下几个方面进一步细分:

地址码长度:1byte / 2byte / 3byte

通信接口类型:I2C / SPI / Microwire / UNIO Bus / Single-Wire

本文的主要研究对象是SPI接口的EEPROM。

2.2 SPI EEPROM内存模型

EEPROM内存单元从大到小一般分为如下4层:Device、Sector、Page、Byte,其中Sector不是必有的,并且Page也只是个结构概念,跟NOR Flash里的Page/Sector意义不一样,因为Byte就是EEPROM读写的最小单元(即可以任意地址随机访问),所以你可以把EEPROM当做一个非易失性的RAM。当然有些高端EEPROM中集成了Page/Sector操作命令,这只是为了让EEPROM操作效率更高而已。

2.3 SPI EEPROM信号与封装

SPI EEPROM一般有8个脚,除去电源Vcc,地GND/Vss,以及SPI四根信号线(CS#, SCK, SI, SO)不言而喻之外,还有两根特殊的控制信号,即WP#(写保护)和HOLD#(挂起)。WP#信号主要是从硬件层面上对EEPROM内存进行保护,防止电路上的噪声干扰篡改了EEPROM里的内容;而HOLD#则提供EEPROM写操作暂停的功能,当该信号有效的时候,SI信号输入将被忽略,因此主机可以做其他更高优先级的事情。

SPI EEPROM虽然只有8pin,但是封装种类还是比较齐全的,这其中最经典的当属JEDEC定义的8-lead SOIC,此外还有TSSOP8, UDFN8, WLCSP8,下图罗列了常见封装:

2.4 SPI EEPROM接口命令

2.4.1 事实标准

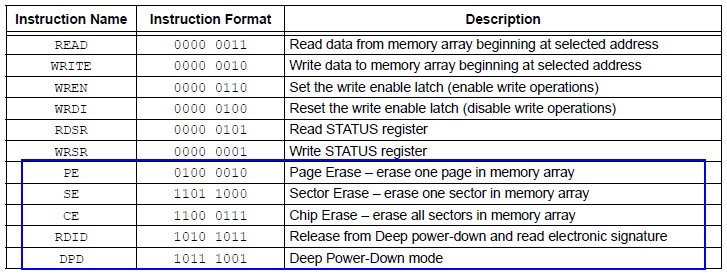

痞子衡在文章开头的时候讲过,SPI EEPROM并没有什么成文的接口命令标准,但是各大厂商生产的SPI EEPROM无一例外都支持下表的6条命令,即READ(读内存)、WRITE(写内存)、WREN(写使能)、WRDI(写禁止)、RDSR(读状态寄存器)、WRSR(写状态寄存器),所以从软件接口层面而言,这6条命令就是SPI EEPROM事实上的接口命令标准。

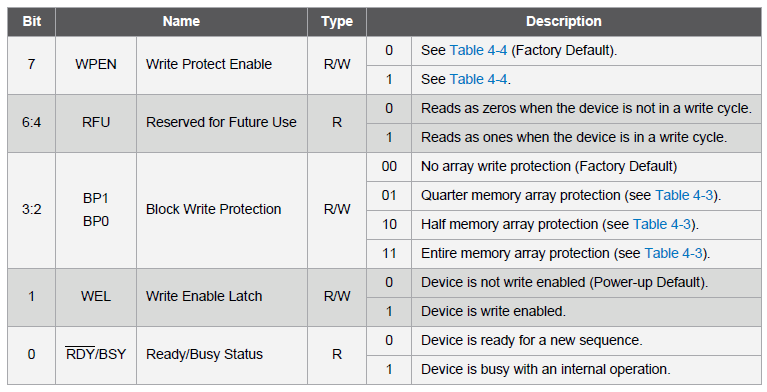

除了6条标准命令外,SPI EEPROM内部还有一个8bit的状态寄存器,用于反馈命令执行状态,这8bit状态寄存器的位定义也是存在如下表所示的事实标准的:

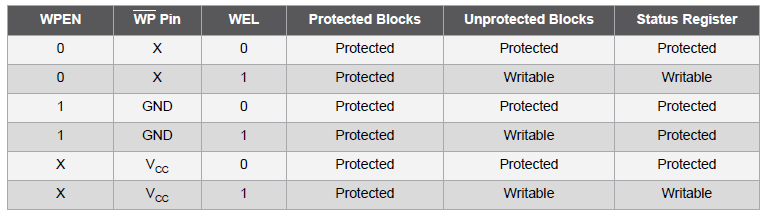

不考虑写保护特性的话,bit0 - RDY#和bit1 - WEL是比较常用的,RDY#位主要用于标示所有涉及改变内存或状态寄存器的命令的执行结果,WEL位则保存了上一次WREN和WRDI命令的执行结果。状态寄存器中的其他两处定义bit7 - WPEN, bit[3:2] - BP[1:0]则主要与写保护特性有关,它们的具体作用如下:

2.4.2 厂商个性化

除了6条事实标准的命令外,有些厂商还实现了一些自定义的命令,这些命令并不一定通用,一般用于较大容量(3byte地址码,512Kb以上)的EEPROM上。痞子衡找了一款非常经典的EEPROM,来自Microchip的25AA系列(25AA1024),让我们看看它有啥个性化的命令。这颗EEPROM容量为1Mb,属于大容量EEPROM,为了提高EEPROM操作效率,Microchip为这颗EEPROM增加了Page/Sector/Chip Erase命令,使得擦除操作效率变高了,如果没有这些个性化擦除命令,那么只能通过标准WRITE命令去手动实现擦除操作,既麻烦又低效。

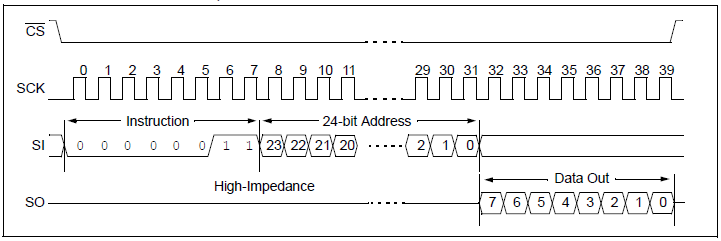

2.5 SPI EEPROM数据速率

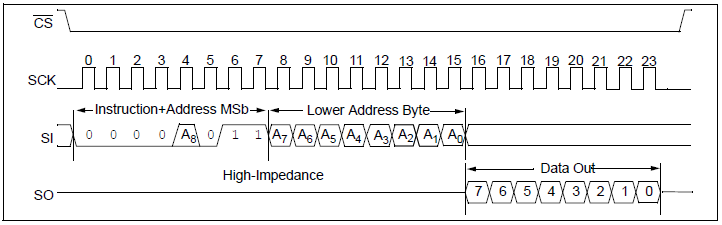

数据存取速率是个重要的技术指标,咱们来看看SPI EEPROM的读写时序,前面痞子衡在讲EEPROM分类的时候提到过EEPROM地址码有1byte/2byte/3byte之分,地址码的区别主要体现了EEPROM读写时序上。对于读时序,在SPI总线发完READ(0x03)命令后,紧接着要发送想要读取的内存地址,地址码不同,发送的地址字节数也不同。对于容量大于512Kb的EEPROM(即地址码为3byte),显然要发送3byte的地址,才能确定要读的数据所在地址,然后才能进行读数据操作。

而对于容量小于等于512Kb的EEPROM,关于1byte和2byte地址码区分,有一个特殊的设计,即对于512byte容量的EEPROM,按容量来说其属于2byte地址码范畴,READ命令后需要发送2byte地址,但实际上只需要发送1byte地址(A7-A0),而最高地址位A8放在了READ命令码bit3里,这样可以节省1个字节的地址码。因此1Kb - 512Kb容量的EEPROM地址码为2byte,512byte及以下容量的EEPROM地址码为1byte,如下图所示:

从上面读时序可以看出,READ命令码和地址码发完之后几乎没有等待周期,就可以直接读取EEPROM中数据,因此EEPROM读数据速率完全取决于SPI总线速率,所以我们只需要打开EEPROM数据手册,看看它最高能支持多高的SPI总线速率即可(常见的有2MHz/5MHz/10MHz/20MHz)。

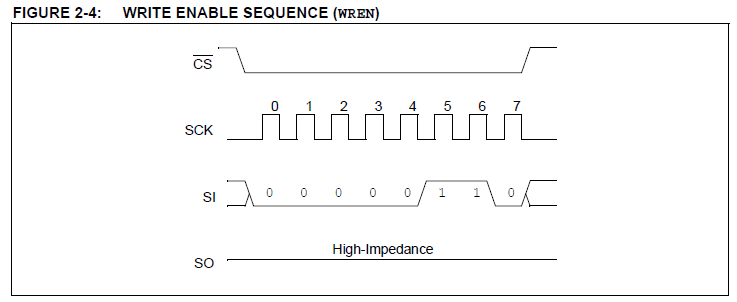

对于写时序,就稍微复杂一些了,这里不考虑地址码区别,以2byte地址为例。首先在发送WRITE命令之前需要发送一个WREN命令使能写操作,因为默认EEPROM在执行完上一次写操作后会恢复写禁止状态,在发送WRITE命令进行写操作之前必须保证EEPROM处于写使能状态。

确保EEPROM进入写使能状态后,开始发送WRITE命令,然后是地址码,接着是要写入的数据,痞子衡前面讲过Page在EEPROM是个结构概念,但其实也跟WRITE命令有关,因为EEPROM既可以按byte去写,也可以按Page去写,如果需要存入连续的数据,显然按Page去写效率比按Byte写入更高。这里需要注意的是,WRITE命令后面跟的字节数不能超过要写入的首地址所在Page剩余的字节数。下图示例的Page写时序最大byte数为16/32,是因为示例EEPROM的page size即16/32 byte。

当一次WRITE时序内要写入的数据全部发送完成之后,底下便进入等待周期,与READ时序不同的是,WRITE时序有等待周期,因为EEPROM内部要将缓存在page buffer里的数据编程到真正的内存空间里,这需要时间。用户只能通过不断地发送如下RDSR命令去读取状态寄存器bit0 - RDY#来判断WRITE等待周期是否结束。因此写时序速率不仅仅取决于SPI总线速率,还取决于等待周期时长。

如果想快捷地了解SPI EEPROM的性能,最简单的就是打开SPI EEPROM手册,看首页的feature介绍,如下是25AA080的简要feature:

• Max. Clock 10 MHz

• 1024 x 8-bit Organization

• 16 Byte Page (‘C’ version devices)

• 32 Byte Page (‘D’ version devices)

• Self-Timed Erase and Write Cycles (5 ms max.)

• Block Write Protection:

- Protect none, 1/4, 1/2 or all of array

• Built-In Write Protection:

- Power-on/off data protection circuitry

- Write enable latch

- Write-protect pin

• Sequential Read

• High Reliability:

- Endurance: > 1M erase/write cycles

- Data retention: > 200 years三、SPI EEPROM产品

最后痞子衡收集了可以售卖SPI EEPROM芯片的厂商及产品系列:

| 厂商 | 芯片系列 | 官方网址 |

|---|---|---|

| Microchip Atmel |

25AA, 25LC AT25 |

https://www.microchip.com spi-eeprom-part-catalog |

| ST | M95 | https://www.stmicroelectronics.com.cn spi-eeprom-part-catalog |

| Onsemi | CAT25 | https://www.onsemi.cn spi-eeprom-part-catalog |

| Renesas | R1EX25 | https://www.renesas.com/ spi-eeprom-part-catalog |

| Rohm | BR25A, BR25G, BR25H, BR25S | https://www.rohm.com spi-eeprom-part-catalog |

| Fudan Micro | FM25 | http://www.fmsh.com spi-eeprom-part-catalog |

至此,EEPROM接口标准及SPI EEPROM痞子衡便介绍完毕了,掌声在哪里~~~

加载全部内容